I have recently started using programmable logic devices (PLDs) in some of my projects. Below are the steps I am using, along with some challenges that I have encountered. As I learn more about PLDs, I will update this post.

My first use of PLDs was for address decode logic to CS/OE lines on my 65816 build. Most recently, I have configured a pair of PLDs for a video card that I am building. In both of these cases, I am using a Lattice GAL22V10D-15LP or -10LP PLD. I have attempted to use the -7LP PLDs, but my programmer fails to work with them (more on that later).

Video Card PLDs

While I will walk through using a PLD for my video card, these same general steps are used for my 65816 address decode logic.

As I looked into programming my PLDs, I found very few options to program them. The primary recommendation I found was to use WinCupl, a rather dated application. CUPL (Compiler for Universal Programmable Logic) is used in WinCupl to develop the logic for the PLD. The CUPL is compiled into a JEDEC file. This JEDEC file must then be written to the PLD. To get me moving along faster, I wanted to use a more graphical option than CUPL to create my logic. For this, I am using Digital, a logic designer and circuit simulator.

For me, the basic process to get a functioning PLD is:

Develop the logic in Digital

From Digital, generate the CUPL

Load the CUPL into WinCupl

From WinCupl, compile the CUPL into a JEDEC file

From Xgpro, load the JEDEC file and write it to the GAL22V10D PLD

Update: Digital has the ability to directly create a JEDEC file. Make sure to assign pin numbers to all inputs and outputs in Digital. Then choose Analysis, Create, GAL..., JEDEC. You can then skip steps 3 and 4 above!

For my video card, I wanted one PLD for generating horizontal timing and one PLD for generating vertical timing. See VGA Card for 65816 PC - Step 1: Basic Circuit. With this in mind, I created the following logic in Digital for the horizontal timing.

To create the CUPL in Digital, the logic must be analyzed. The CUPL can then be saved.

For the initial logic I posted earlier, this is where I ran into a problem. Digital cannot analyze circuits with loops -- in this case, the SR latches on the right. I worked around it by modifying the circuit as follows. This requires two pins on the PLD to be connected together -- a bit wasteful. (Is there a better way to do this?)

The generated CUPL looks something like this:

This CUPL can then be loaded into WinCupl. Unfortunately, this is where I encountered another issue. Directly opening the above CUPL in WinCupl causes it to crash -- no errors, the application just disappears. I worked around this by creating a new, blank file in WinCupl and pasting in the CUPL section by section.

Update: u/tmrob4 suggested moving the CUPL files to the WinCupl installation folder. This seems to be helping nicely!

I select the device and save the file. There was no option for my specific GAL22V10D, so I chose something that appeared to be the closest.

Then I run Device Dependent Compile. If I'm lucky, it will compile. More often than not, I get an error "Key is not unique in collection" and WinCupl crashes (which seems to be a common pattern with this software). I have not been able to pin down the root cause of this error yet. Whether or not it truly helps, I'm not sure, but if I restart Windows and try it again, I have better odds of getting WinCupl to generate the JEDEC file.

Update: u/tmrob4 suggested deselecting "Project" in the View menu. While I already had that deselected, if you're encountering this issue, it might be worth checking.

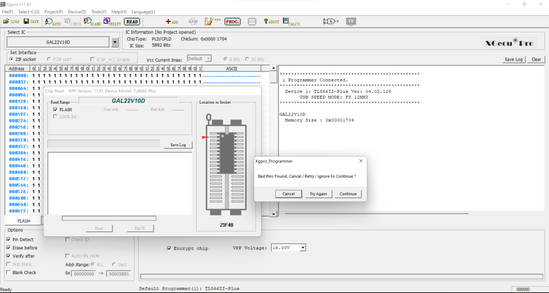

Assuming a JEDEC does get generated, it can then be programmed to the PLD device. I am using a TL866II-Plus with the manufacturer-provided software, Xgpro.

Repeat the above steps for the vertical sync PLD.

I have had no issues programming GAL22V10D-15LP and GAL22V10D-10LP PLDs with my programmer. Unfortunately, I have not been able to get -7LP PLDs to program; I get errors on pin 2 (with different PLDs). I have reached out to the manufacturer of the programmer but have received no response; I can't imagine supporting end-of-life PLDs is high on their priority list (if it's even a programmer issue).

VHDL?

I notice in WinCupl there is an option to open VHDL. I have yet to determine if this is simply a text editor for VHDL or if the program is supposed to support converting VHDL to CUPL. With a little searching, I found some references to an add-in being required. Digital can export VHDL, but WinCupl crashes when I try to load VHDL -- and it deletes the source VHDL file in the process!

Converting Truth Tables to CUPL

Another nice feature of Digital that I used for my 65816 logic was to pull in a truth table from Excel. Digital can then generate the logic based on the truth table, along with the CUPL based on the truth table.

I need to look into Digital... writing CUPL is irritating, that'd be great if I can draw it and have the software generate it.